MC68HC05i8/D Rev. 1

# High-density Complementary Metal Oxide Semicorol (HCMOS) Microcomputer Unit

an This document contains information on a new product. Specifications and information herein are subject to change without notice.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🖗 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

All Trade Marks recognised.

© MOTOROLA LTD., 1992

# **Table of Contents**

| Paragra<br>Number |                                      | Page<br>Number |

|-------------------|--------------------------------------|----------------|

|                   | INTRODUCTION                         | 1-1            |

| 1.1<br>1.2        | FEATURES                             | 21-1           |

| 1.2               |                                      | 1-2            |

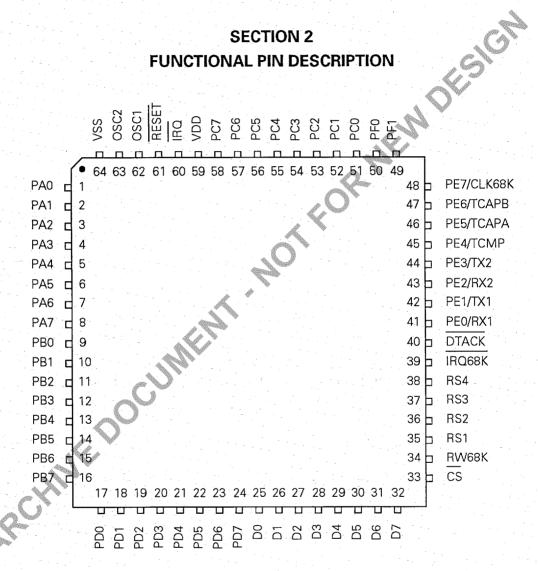

|                   | FUNCTIONAL PIN DESCRIPTION           | 2-1            |

| 2.1               | VDD AND VSS                          | 22             |

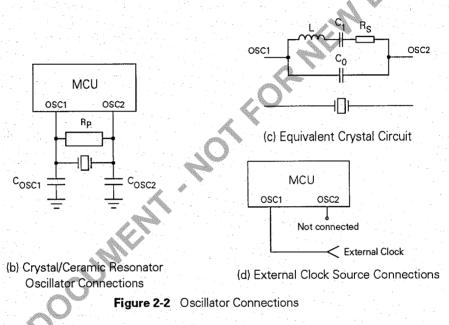

| 2.1               | OSC1/OSC2                            | 2-2<br>2-2     |

| 2.2.1             |                                      | 2-2<br>2-2     |

| 2.2.2             | Ceramic Resonator                    | 2-2            |

| 2.2.3             |                                      |                |

| 2.3               | BESET                                | 2-3            |

| 2.4               | IRQ                                  | 2-3            |

| 2.5               | I/O PORT PINS<br>Ports A–D (Px0–Px7) | 2-4            |

| 2.5.1             | Ports A–D (Px0–Px7)                  | 2-4            |

| 2.5.2             | Port E (PE0-PE7)                     | 2-4            |

| 2.5.3             |                                      | 2-4            |

| 2.6               |                                      | 2-4            |

| 2.6.1<br>2.6.2    |                                      |                |

| 2.6.2             | RC1_RC1                              | 2-4<br>2-5     |

| 2.6.4             | <u>RW</u> 68K                        | 2-5            |

| 2.6.5             |                                      | 2-5            |

| 2.6.6             |                                      |                |

| 2.6.7             |                                      |                |

| 2.7               | 16-BIT PROGRAMMABLE TIMER PINS       |                |

| 2.7.1             |                                      | 2-5            |

| 2.7.2             | ТСАРА, ТСАРВ                         | 2-5            |

| 2.8               |                                      |                |

| 2.8.1             |                                      |                |

| 2.8.2             | TX1, TX2                             | 2-6            |

MOTOROLA

Paragraph Number

# Page Number

# CPU CORE AND INSTRUCTION SET

| 승규가 집에 가장 같은 것이 같은 것이 가 있는 것이 것을 다 가지 않는 것이 같은 것이 같은 것이 가지 않는 것이 것을 수 있는 것이 같이 없다.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

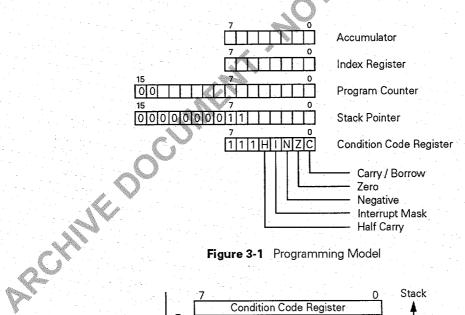

| 3.1 REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

| 211 Accumulator (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2         |

| 3.1.2     Index Register (X)       3.1.3     Program Counter (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-2         |

| 3.1.3 Program Counter (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| 3.1.4 Stack Pointer (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-2         |

| 3.1.5 Condition Code Register (CCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |

| 3.1.5.1 Half carry (H)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

| 3.1.5.2 Interrupt (I)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-3         |

| 3.1.5.3 Negative (N)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-3         |

| 3.1.5.3         Negative (N)           3.1.5.4         Zero (Z)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| 3.1.5.5 Carry/Borrow (C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 3.1.5.5 Carry/Borrow (C)<br>3.2 INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| 3.2.1 Register/Memory Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>3-</b> A |

| 3.2.2 Branch Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

| 3.2.3 Bit Manipulation Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-4         |

| 3.2.2       Branch Instructions         3.2.3       Bit Manipulation Instructions         3.2.4       Read/Modify/Write Instructions                                                                                                                                                                                                                                                                                                                                                                                                                   |             |

| 375 CONTROLINSTRUCTIONS 🐘 🐘                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-4         |

| 3.2.6 Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-4         |

| 3.2.6 Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 3.3.1 Inherent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| 3.3.2 Immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

| 3.3.3 Direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 3 3 4 Fxtended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| 3.3.5 Indexed, No Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 3.3.6 Indexed, 8-bit Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

| 3.3.7 Indexed, 16-bit Offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

| 3.3.8 Belative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13        |

| 3.3.9 Bit Set/Clear<br>3.3.10 Bit Test and Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |

| 3.3.10 Bit Test and Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

| 2019년 🗰 🌋 : ''' 2019년 1월 2019년 |             |

# Paragraph Number

# Title

# Page Number

# **RESETS, INTERRUPTS AND LOW POWER MODES**

| 4.1 RESETS                                           |       |

|------------------------------------------------------|-------|

| 4.1.1 Power-on Reset                                 | . 4-2 |

| 4.1.1 Power-on Reset                                 | 4-2   |

| 4.1.3 Illegal Address Reset                          | 4-2   |

| 4.1.4 Computer Operating Properly (COP) Reset        | . 4-2 |

| 4.2 INTERRUPTS                                       |       |

| 4.2.1 Non-Maskable Software Interrupt (SWI)          |       |

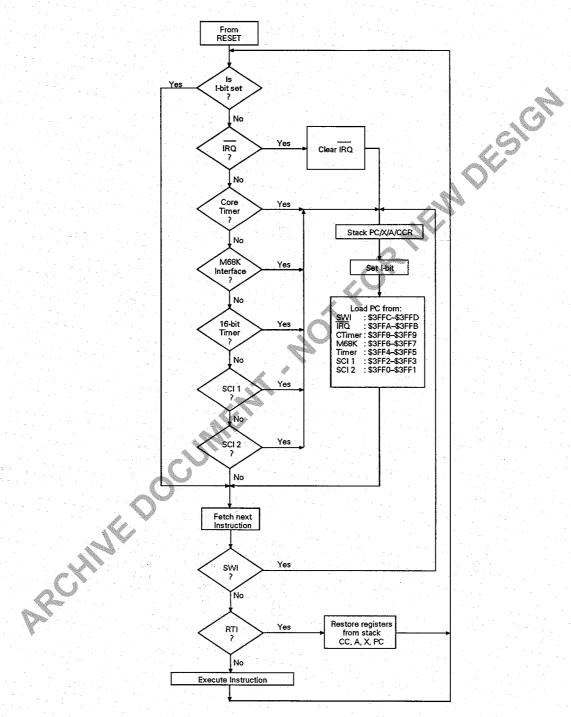

| 4.2.2 Maskable Hardware Interrupts                   | . 4-4 |

| 4.2.2.1 External Interrupt (IRQ)                     |       |

| 4.2.2.2 Real Time and Core Timer (CTIMER) Interrupts | . 4-4 |

| 4.2.2.3 M68000 Interrupt                             | . 4-4 |

| 4.2.2.4 Programmable 16-bit Timer Interrupt          | 4-5   |

| 4.2.2.5 SCI1 Interrupt                               | . 4-5 |

|                                                      | . 4-5 |

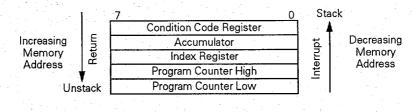

| 4.2.3 Hardware Controlled Interrupt Sequence         | . 4-5 |

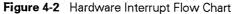

| 4.3 LOW POWER MODES                                  | 4-6   |

| 4.3.1 STOP                                           | . 4-6 |

| 4.3.2 WAIT                                           | . 4-6 |

| 4.3.3 Data Retention Mode                            | . 4-6 |

|                                                      |       |

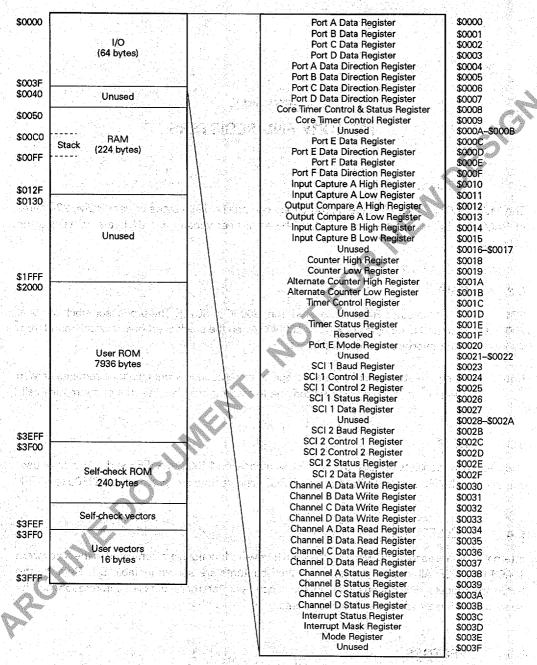

# MEMORY AND REGISTERS

5.1

MEMORY MAP

5-1

5.2

RAM

5-1

5.3

ROM

5-1

5.4

REGISTERS

5-1

5.5

VECTORS

5-1

5-1

Paragraph Number

Title

# Page Number

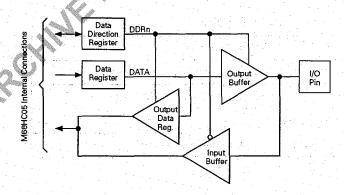

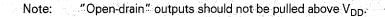

# PARALLEL INPUT/OUTPUT PORTS

| 6.1 INPUT/OUTPUT PROGRAMMING                                                                                    | 6-1 |

|-----------------------------------------------------------------------------------------------------------------|-----|

| 그는 것 같은 실험을 그 같은 잘 집을 했다. 것은 것 같은 것 같은 것은 것은 가지가 하는 것이라. 한 것을 것을 하는 것 같은 것을 하는 것 같은 것 같이 하는 것 같은 것 같이 하는 것 같은 것 | 6-2 |

|                                                                                                                 | 6-2 |

| 6.4 PORT F                                                                                                      | 6÷2 |

|                                                                                                                 | 6-3 |

| 6.5.1 Port A-Port D Data Registers                                                                              | 6-3 |

| 6.5.2 Port E Data Register                                                                                      | 6-3 |

| 6.5.3 Port F Data Register                                                                                      | 6-3 |

| 6.5.4 Ports A–D Data Direction Register (Port x DDR)                                                            | 6-3 |

| 6.5.5 Port E Data Direction Register (Port E DDR)                                                               | 6-3 |

| 6.5.6 Port E Mode Register                                                                                      | 6-4 |

| 6.5.6.1 CK68 — External clock mode for the M68000 unit                                                          | 6-4 |

| 6.5.6.2 TCAPB — Input Capture B                                                                                 | 6-4 |

|                                                                                                                 | 6-4 |

| 6.5.6.4 TCMP — Output Compare                                                                                   | 6-4 |

| 6.5.6.5 WOM0-3 Wired-OR mode                                                                                    | 6-5 |

| 6.5.7 Port F Data Direction Register (Port F DDR)                                                               | 6-5 |

| 6.6 OTHER PORT CONSIDERATIONS                                                                                   | 6-6 |

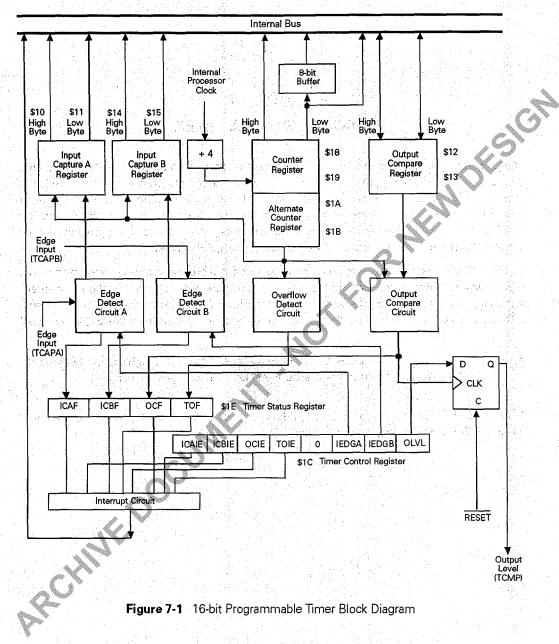

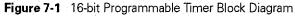

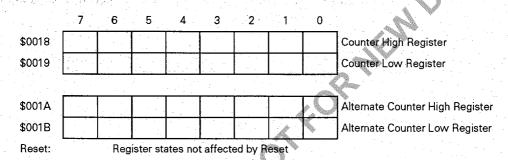

# **PROGRAMMABLE TIMER**

7.1 COUNTER 7:1:1 7.2 7.2:1 7.2.1.1 ICAIE — Input Capture A Interrupt Enable 7.2.1.2 7.2.1.3 7.2.1.4 7.2.1.5 7.2.1.6 7.2.1.7 7.2.2 7.2.2.1 7.2.2.2 ICBF — Input Capture B Status Flag 7.2.2.3 7.2.2.4

7-1

### Paragraph Page Number Title Number 723 Input Capture Function 7.7 7.2.3.1 7.2.3.2 7.2.4 7241 7.3 7.4 75

# CORE TIMER

REAL TIME INTERBUPTS (BTI) 8.1 8-2 8.2 8.3 8.3.1 8.3.1.1 8.3.1.2 8.3.1.3 8.3.1.4 8.3.1.5 8.3.2 8.4 CORE TIMER DURING STOP ...... 8-5 8.5

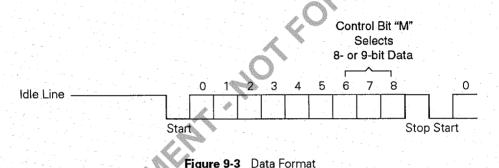

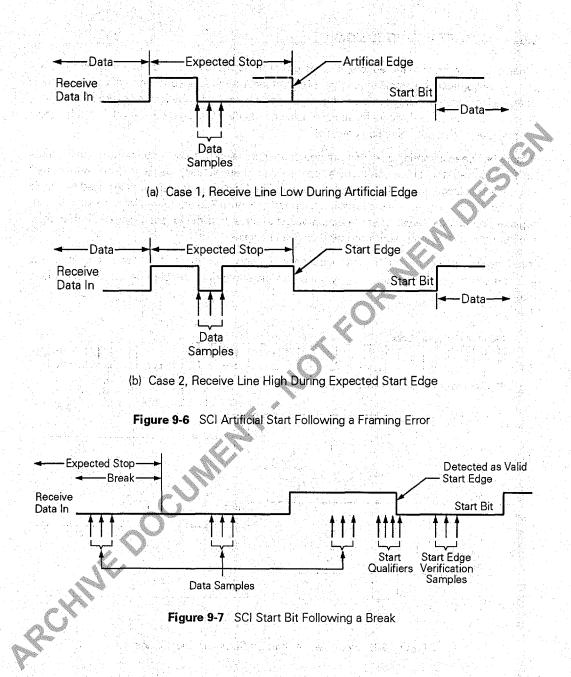

# SERIAL COMMUNICATIONS INTERFACE

DVERVIEW AND FEATURES 9-1 94 9,1.1 9.1.2 9.1.3 9.2 9.3 RECEIVER WAKE-UP OPERATION 9-5 9.4 941 942 9.5 9.6 9.7

MC68HC05i8

8-1

9-1

| 9.8       SCI REGISTERS       9-9         9.8.1       Serial Communications Data Register (SCDR)       9-9         9.8.2       Serial Communications Control Register 1 (SCCR1)       9-9         9.8.2.1       R8       Receive Data Bit 8       9-10         9.8.2.2       T8       Transmit Data Bit 8       9-10         9.8.2.3       M       Mode (select character format)       9-10         9.8.2.4       WAKE       Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE       Transmit Interrupt Enable       9-11         9.8.3.2       TCIE       Transmit Complete Interrupt Enable       9-11         9.8.3.4       ILIE       Idle Line Interrupt Enable       9-11         9.8.3.5       TE       Transmitter Enable       9-11         9.8.3.6       RE       Receiver Interrupt Enable       9-11         9.8.3.6       RE       Serial Communications Status Register (SCSR)       9-12         9.8.4       Serial Communications Status Register FOSR)       9-12         9.8.4.3       RDRF       Receive Data Register Full Flag       9-13         9.8.4.4       IDLE       IDLE       IDLE       9-13                                                                                           | Paragraph<br>Number       | Title                                            | Page<br>Number |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------|----------------|

| 9.8.2.1       R8 — Receive Data Bit 8       9-10         9.8.2.2       T8 — Transmit Data Bit 8       9-10         9.8.2.3       M — Mode (select character format)       9-10         9.8.2.4       WAKE — Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE — Transmit Interrupt Enable       9-11         9.8.3.2       TCIE — Transmit Complete Interrupt Enable       9-11         9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Kake-up       9-12         9.8.3.7       RWU — Receiver Wake-up       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9                                                        | 98 50                     | 1 BEGISTERS                                      | 00             |

| 9.8.2.1       R8 — Receive Data Bit 8       9-10         9.8.2.2       T8 — Transmit Data Bit 8       9-10         9.8.2.3       M — Mode (select character format)       9-10         9.8.2.4       WAKE — Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE — Transmit Interrupt Enable       9-11         9.8.3.2       TCIE — Transmit Complete Interrupt Enable       9-11         9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Kake-up       9-12         9.8.3.7       RWU — Receiver Wake-up       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9                                                        |                           | Serial Communications Data Register (SCDR)       | 9-9<br>00      |

| 9.8.2.1       R8 — Receive Data Bit 8       9-10         9.8.2.2       T8 — Transmit Data Bit 8       9-10         9.8.2.3       M — Mode (select character format)       9-10         9.8.2.4       WAKE — Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE — Transmit Interrupt Enable       9-11         9.8.3.2       TCIE — Transmit Complete Interrupt Enable       9-11         9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Kake-up       9-12         9.8.3.7       RWU — Receiver Wake-up       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9                                                        |                           | Serial Communications Data negister (SCDI)       |                |

| 9.8.2.2       T8 — Transmit Data Bit 8       9-10         9.8.2.3       M — Mode (select character format)       9-10         9.8.2.4       WAKE — Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE — Transmit Interrupt Enable       9-11         9.8.3.2       TCIE — Transmit Complete Interrupt Enable       9-11         9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Interrupt Enable       9-11         9.8.3.7       RWU — Receiver Enable       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data-Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag                                                          | 이내는 것은 것을 가지 않는 것을 많이 했다. |                                                  |                |

| 9.8.2.3       M — Mode (select character format)       9-10         9.8.2.4       WAKE — Wake-up Mode Select       9-10         9.8.3       Serial Communications Control Register 2 (SCCR2)       9-10         9.8.3.1       TIE — Transmit Interrupt Enable       9-11         9.8.3.2       TCIE — Transmit Complete Interrupt Enable       9-11         9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Interrupt Enable       9-11         9.8.3.7       RWU — Receiver Enable       9-11         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Complete Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag       9-13 <td></td> <td>T8 - Transmit Data Bit 8</td> <td>0 10</td> |                           | T8 - Transmit Data Bit 8                         | 0 10           |

| 9.8.2.4       WAKE — Wake-up Mode Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           | M — Mode (select character format)               |                |

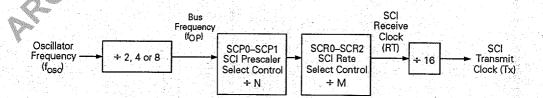

| 9.8.3Serial Communications Control Register 2 (SCCR2)9-109.8.3.1TIE — Transmit Interrupt Enable9-119.8.3.2TCIE — Transmit Complete Interrupt Enable9-119.8.3.3RIE — Receiver Interrupt Enable9-119.8.3.4ILIE — Idle Line Interrupt Enable9-119.8.3.5TE — Transmitter Enable9-119.8.3.6RE — Receiver Enable9-119.8.3.7RWU — Receiver Enable9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-139.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           | WΔKF — Wake un Mode Select                       |                |

| 9.8.3.1TIE — Transmit Interrupt Enable9-119.8.3.2TCIE — Transmit Complete Interrupt Enable9-119.8.3.3RIE — Receiver Interrupt Enable9-119.8.3.4ILIE — Idle Line Interrupt Enable9-119.8.3.5TE — Transmitter Enable9-119.8.3.6RE — Receiver Enable9-119.8.3.7RWU — Receiver Wake-up9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-139.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           | Serial Communications Control Begister 2 (SCCB2) | 9-10           |

| 9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Enable       9-12         9.8.3.7       RWU — Receiver Wake-up       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.5       Baud Rate Register (BAUD)       9-14         9.8.5.1       SCP1, SCP0 — Serial Prescaler Select bits       9-14                                                                                                                                                                                                                        |                           | TIF — Transmit Interrunt Enable                  | 9-11           |

| 9.8.3.3       RIE — Receiver Interrupt Enable       9-11         9.8.3.4       ILIE — Idle Line Interrupt Enable       9-11         9.8.3.5       TE — Transmitter Enable       9-11         9.8.3.6       RE — Receiver Enable       9-12         9.8.3.7       RWU — Receiver Wake-up       9-12         9.8.3.8       SBK — Send Break       9-12         9.8.4       Serial Communications Status Register (SCSR)       9-12         9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-13         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.5       Baud Rate Register (BAUD)       9-14         9.8.5.1       SCP1, SCP0 — Serial Prescaler Select bits       9-14                                                                                                                                                                                                                        |                           | TCIE — Transmit Complete Interrupt Enable        | 9-11           |

| 9.8.3.7HWO — Receiver Wake-up9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.8.3.3                   | RIE Receiver Interrupt Enable                    | 9-11           |

| 9.8.3.7HWO — Receiver Wake-up9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.8.3.4                   | ILIE — Idle Line Interrupt Enable                | 9-11           |

| 9.8.3.7HWO — Receiver Wake-up9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.8.3.5                   | TE — Transmitter Enable                          |                |

| 9.8.3.7HWO — Receiver Wake-up9-129.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9.8.3.6                   | RE — Receiver Enable                             |                |

| 9.8.3.8SBK — Send Break9-129.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.8.3.7                   |                                                  |                |

| 9.8.4Serial Communications Status Register (SCSR)9-129.8.4.1TDRE — Transmit Data Register Empty Flag9-129.8.4.2TC — Transmit Complete Flag9-139.8.4.3RDRF — Receive Data Register Full Flag9-139.8.4.4IDLE — Idle Line Detected Flag9-139.8.4.5OR — Overrun Error Flag9-139.8.4.6NF — Noise Error Flag9-139.8.4.7FE — Framing Error Flag9-139.8.5Baud Rate Register (BAUD)9-149.8.5.1SCP1, SCP0 — Serial Prescaler Select bits9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9.8.3.8                   | SBK — Send Break                                 |                |

| 9.8.4.1       TDRE — Transmit Data Register Empty Flag       9-12         9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.5       Baud Rate Register (BAUD)       9-14         9.8.5.1       SCP1, SCP0 — Serial Prescaler Select bits       9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9.8.4                     | Serial Communications Status Register (SCSR)     |                |

| 9.8.4.2       TC — Transmit Complete Flag       9-13         9.8.4.3       RDRF — Receive Data Register Full Flag       9-13         9.8.4.4       IDLE — Idle Line Detected Flag       9-13         9.8.4.5       OR — Overrun Error Flag       9-13         9.8.4.6       NF — Noise Error Flag       9-13         9.8.4.7       FE — Framing Error Flag       9-13         9.8.5       Baud Rate Register (BAUD)       9-14         9.8.5.1       SCP1, SCP0 — Serial Prescaler Select bits       9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9.8.4.1                   | TDRE — Transmit Data Register Empty Flag         |                |

| 9.8.4.4         IDLE — Idle Line Detected Flag         9-13           9.8.4.5         OR — Overrun Error Flag         9-13           9.8.4.6         NF — Noise Error Flag         9-13           9.8.4.7         FE — Framing Error Flag         9-13           9.8.5         Baud Rate Register (BAUD)         9-14           9.8.5.1         SCP1, SCP0 — Serial Prescaler Select bits         9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9.8.4.2                   | TC — Transmit Complete Flag                      |                |

| 9.8.4.5         OR — Overrun Error Flag         9-13           9.8.4.6         NF — Noise Error Flag         9-13           9.8.4.7         FE — Framing Error Flag         9-13           9.8.5         Baud Rate Register (BAUD)         9-14           9.8.5.1         SCP1, SCP0 — Serial Prescaler Select bits         9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9.8.4.3                   | RDRF — Receive Data Register Full Flag           | 9-13           |

| 9.8.4.6         NF — Noise Error Flag         9-13           9.8.4.7         FE — Framing Error Flag         9-13           9.8.5         Baud Rate Register (BAUD)         9-14           9.8.5.1         SCP1, SCP0 — Serial Prescaler Select bits         9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9.8.4.4                   | IDLE — Idle Line Detected Flag                   | 9-13           |

| 9.8.4.7         FE — Framing Error Flag         9-13           9.8.5         Baud Rate Register (BAUD)         9-14           9.8.5.1         SCP1, SCP0 — Serial Prescaler Select bits         9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                           | OR — Overrun Error Flag                          |                |

| 9.8.5       Baud Rate Register (BAUD)       9-14         9.8.5.1       SCP1, SCP0 — Serial Prescaler Select bits       9-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                           |                                                  |                |

| 9.8.5.1 SCP1, SCP0 — Serial Prescaler Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                           |                                                  |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |                                                  |                |

| 9.8.5.2 SCR2, SCR1, SCR0 — SCI Rate Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                           |                                                  |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9.8.5.2                   | SCR2, SCR1, SCR0 — SCI Rate Select bits          |                |

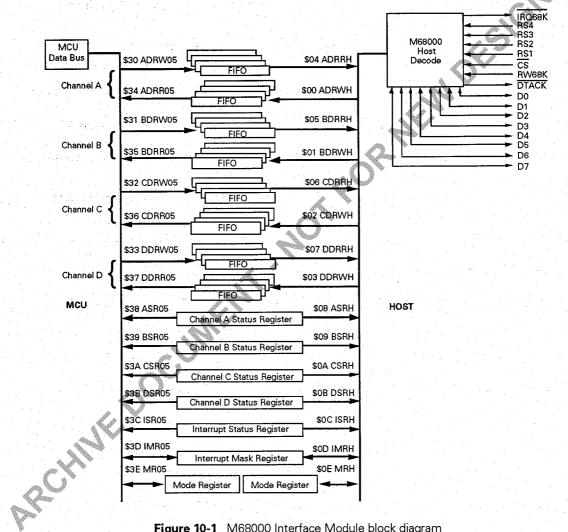

# M68000 INTERFACE MODULE

出自由主要的法

10-1

| 10.1 M68000 BUS INTERFACE PIN DESCRIPTIONS | 0-1 |

|--------------------------------------------|-----|

| 10.111 DTACK                               | 0-1 |

| 10.1.2 IRO68K                              | 0-1 |

| 10.1.3 RS1–RS4                             | 0-1 |

| 10.1.4 RW68K                               | 0-2 |

| 10.1.5 <u>CL</u> K68K                      | 0-2 |

| 10.1.6 CS                                  | 0-2 |

| 10.1.7 Data Bus Lines (D0–D7) 1            | 0-2 |

| 10.2 DATA ACKNOWLEDGE (DTACK) DELAY        | 0-2 |

| 10.3 INTERRUPT ACKNOWLEDGE CYCLE1          | 0-3 |

NE

# Table of Contents (Concluded)

| Paragrap | h                                 |      |       |               |            | Page                   |

|----------|-----------------------------------|------|-------|---------------|------------|------------------------|

| Number   | Titl                              | е    |       |               |            | Number                 |

| 10.1     | NATA AND CONTROL OTATUS DECIS     | TEDO |       |               |            |                        |

|          | DATA AND CONTROL/STATUS REGIS     |      | ••••• |               |            | 10-4                   |

| 10.4.1   | MCU Channel Data Write Registers  |      |       |               |            |                        |

|          | MCU Channel Data Read Registers   |      |       | de la seconda | <u>.</u> ( |                        |

|          | Host Channel Data Write Registers |      |       |               | ··· Kito   | 405 <sup>00</sup><br>4 |

|          | Host Channel Data Read Registers  |      |       |               | $\sim$     | 10-6                   |

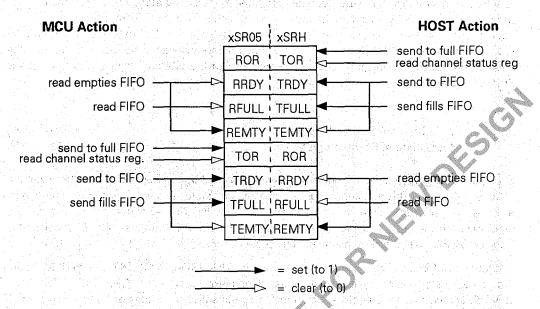

| 10.4.2   | MCU Channel Status Registers      |      |       |               | $\sim$     |                        |

|          | Host Channel Status Registers     |      |       |               | <u>)</u>   | 10-7                   |

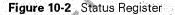

| 10.4.3   | MCU Interrupt Status Register     | -    |       |               |            |                        |

|          | Host Interrupt Status Register    |      |       |               |            | 10-10                  |

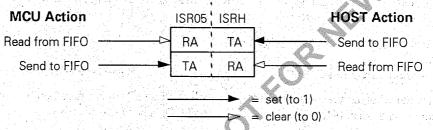

| 10.4.4   | MCU Interrupt Mask Register       |      |       | Manual Street |            |                        |

|          | Host Interrupt Mask Register      |      | Q     |               |            | 10-11                  |

| 10.4.5   | MCU Mode Register                 |      |       | >             |            | 10-12                  |

| 10.4.6   | Host Mode Register                |      |       |               |            | 10-13                  |

|          |                                   |      | W     |               |            |                        |

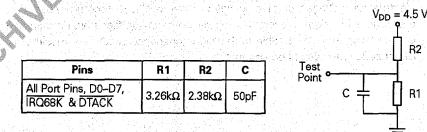

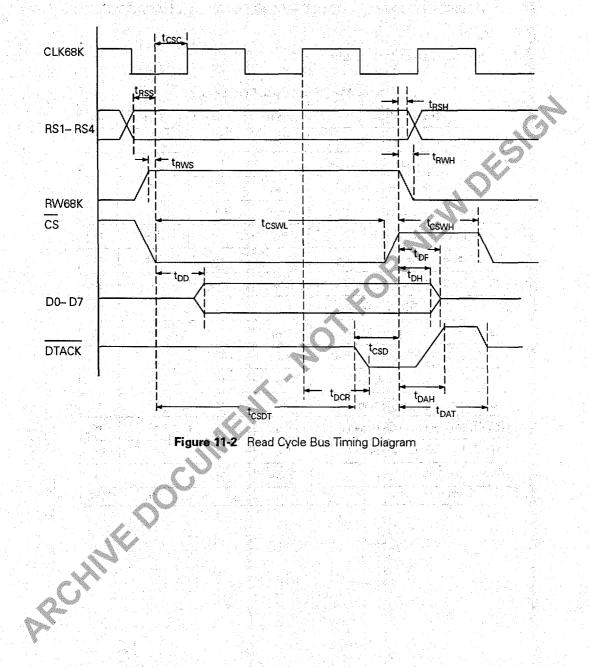

# ELECTRICAL SPECIFICATIONS 11-1

| 11.1   | MAXIMUM RATINGS                                         | 11-1 |

|--------|---------------------------------------------------------|------|

| 11.2   | THERMAL CHARACTERISTICS AND POWER CONSIDERATIONS        | 11-2 |

| 11.3   | DC ELECTRICAL CHARACTERISTICS                           | 11-3 |

| 11.4   | AC ELECTRICAL CHARACTERISTICS                           | 11-4 |

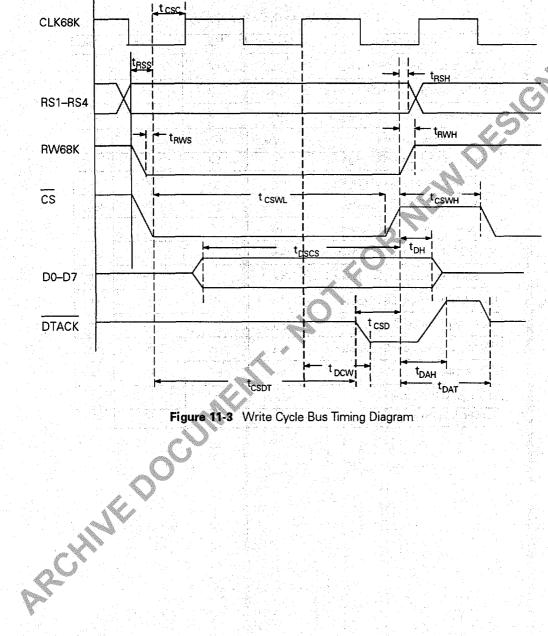

| 11.5   | M68000 INTERFACE MODULE - AC ELECTRICAL CHARACTERISTICS | 11-5 |

| 11.5.1 | Host Read Cycle Bus Timing                              | 11-5 |

| 11.5.2 | HOST Write Cycle Bus Timing                             | 11-7 |

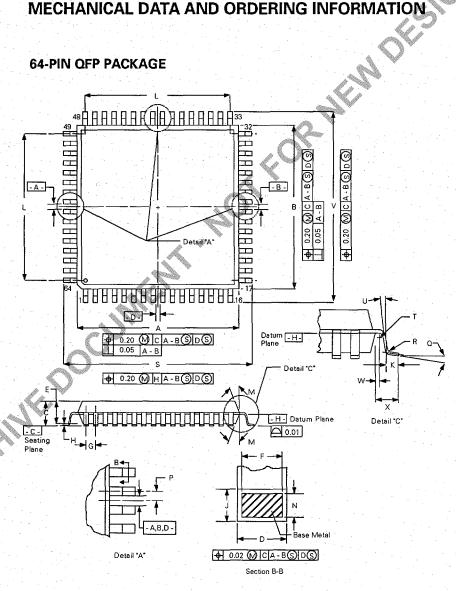

# MECHANICAL DATA AND ORDERING INFORMATION 12-1

| 12.1 64-PIN QFP PACKAGE              | 12-1       |

|--------------------------------------|------------|

| 12.2 ORDERING INFORMATION            | <br>12-3   |

| 12.2.1 EPROMs                        | <br>. 12-3 |

| 12.2.2 Verification media            | <br>. 12-3 |

| 12.2.3 ROM Verification Units (RVUs) | <br>12-3   |

| 12.2.4 MC Order Numbers              | <br>12-3   |

|                                      |            |

#

8.54

THIS PAGE INTENTIONALLY LEFT BLANK

140

MC68HC05i8

14.11

RHENDLOL

**建构成的人民和国际的制度** 医外侧肌 建立的 网络普通马拉斯 化原料

# List of Figures

# Figure Number

# Page Number

|                   |      |                                                                           | 100000                                                                                                                                                                                                                                                                                                                                                |

|-------------------|------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

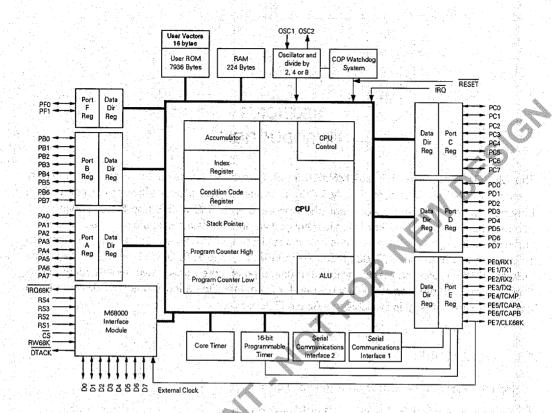

|                   | -1-1 | Functional Block Diagram                                                  | 1-2                                                                                                                                                                                                                                                                                                                                                   |

|                   | 2-1  | Pinout for 64-pin QFP (Quad Flat Pack)<br>Oscillator Connections          |                                                                                                                                                                                                                                                                                                                                                       |

|                   | 2-2  | Oscillator Connections                                                    | 2-3                                                                                                                                                                                                                                                                                                                                                   |

|                   | 3-1  | Programming Model                                                         | 3-1                                                                                                                                                                                                                                                                                                                                                   |

|                   | 3-2  | Stacking Order                                                            | 3-1                                                                                                                                                                                                                                                                                                                                                   |

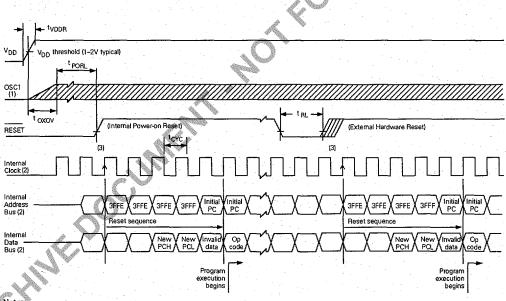

|                   | 4-1  | Programming Model<br>Stacking Order<br>Power-on Reset and RESET           | 4-1                                                                                                                                                                                                                                                                                                                                                   |

| tere i j          | 4-2  |                                                                           |                                                                                                                                                                                                                                                                                                                                                       |

| 1.11              | 4-3  | STOP/WAIT Flow Chart                                                      | 4-8                                                                                                                                                                                                                                                                                                                                                   |

|                   | 5-1  | STOP/WAIT Flow Chart<br>Memory Map of the MC68HC05i8                      | 5-2                                                                                                                                                                                                                                                                                                                                                   |

|                   | 6-1  | Bi-directional I/O Port Structure Block Diagram                           | 6-1                                                                                                                                                                                                                                                                                                                                                   |

| te se la          | 6-2  | Port Logic Levels                                                         | 6-6                                                                                                                                                                                                                                                                                                                                                   |

| 1 - 1 - 1 - 1 - 1 | 7-1  | Port Logic Levels<br>16-bit Programmable Timer Block Diagram              |                                                                                                                                                                                                                                                                                                                                                       |

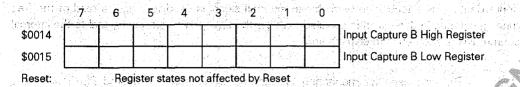

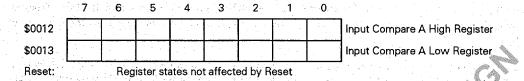

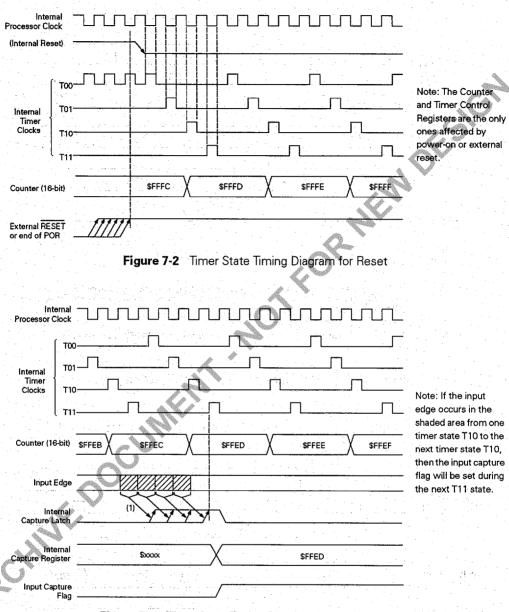

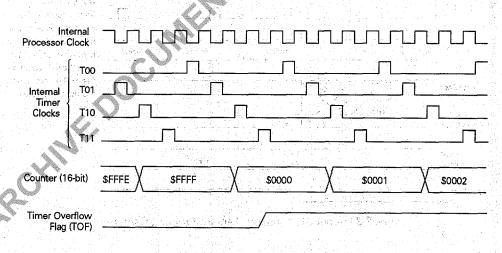

|                   | 7-2  | Timer State Timing Diagram for Reset                                      | 7-11                                                                                                                                                                                                                                                                                                                                                  |

|                   | 7-3  | Timer State Timing Diagram for Input Captures                             | 7-11                                                                                                                                                                                                                                                                                                                                                  |

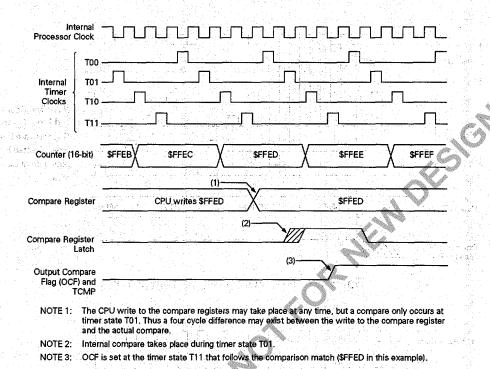

|                   | 7-4  | Timer State Timing Diagram for Output Compare                             | 7-12                                                                                                                                                                                                                                                                                                                                                  |

|                   | 7-5  | Timer State Timing Diagram for Timer Overflow                             | 7-12                                                                                                                                                                                                                                                                                                                                                  |

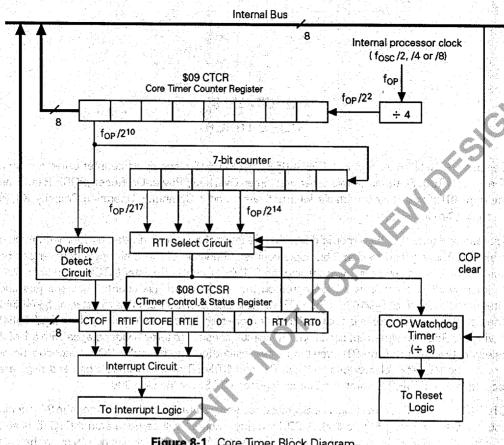

|                   | 8-1  | Core Timer Block Diagram<br>Serial Communications Interface Block Diagram | 8-2                                                                                                                                                                                                                                                                                                                                                   |

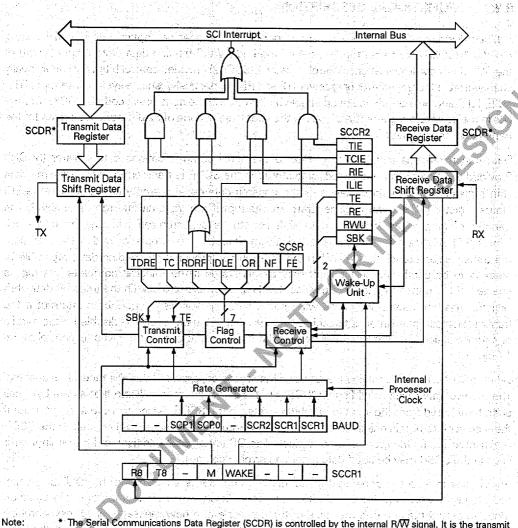

|                   | 9-1  | Serial Communications Interface Block Diagram                             | 9-4                                                                                                                                                                                                                                                                                                                                                   |